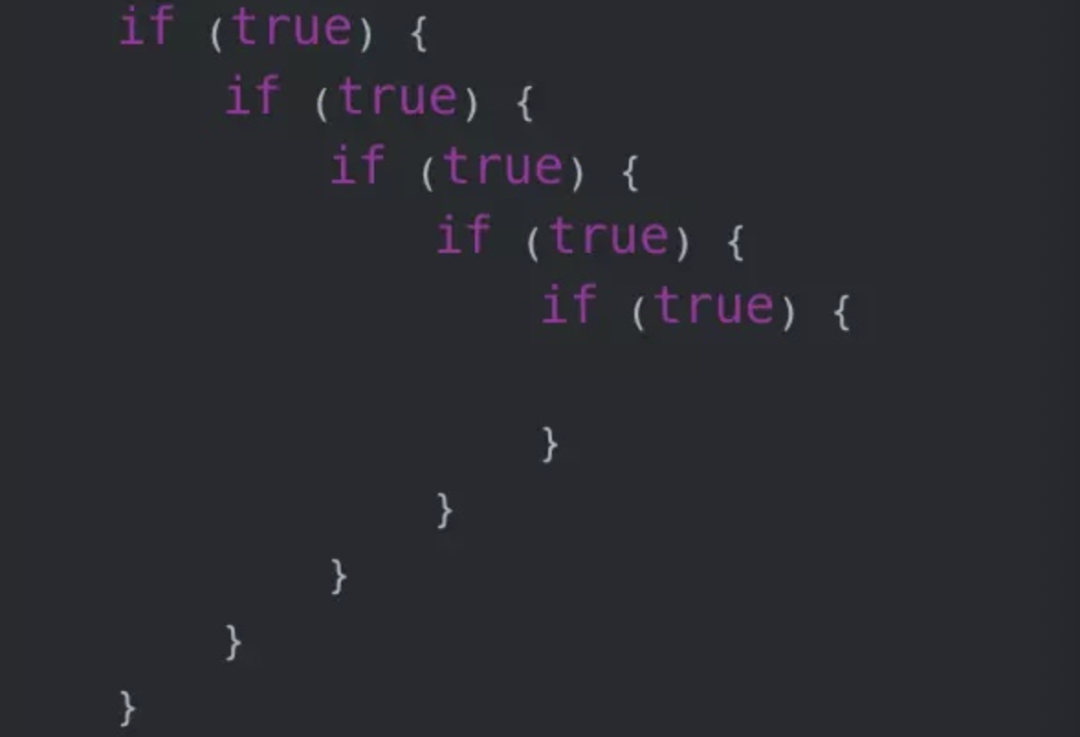

本文记录了作者从“代码优化”到“过度设计”的典型思考过程,这过程中涉及了很多Java的语法糖及设计模式的东西,很典型,能启发思考,遂记录下来。 有一天Review师妹的代码,看到一行很难看的

2024-01-19 10:05

观点一(灵剑): 前期迭代懒得优化,来一个需求,加一个if,久而久之,就串成了一座金字塔。 当代码已经复杂到难以维护的程度之后,只能狠下心重构优化。那,有什么方案可以优雅的优化

2023-06-22 10:01

代码优化,一些细小的地方有什么好修改的,改与不改对于代码的运行效率有什么影响呢?

2020-03-08 08:31

对程序进行优化,通常是指优化程序代码或程序执行速度。优化代码和优化速度实

2018-07-24 10:31

选择一种合适的数据结构很重要,如果在一堆随机存放的数中使用了大量的插入和删除指令,那使用链表要快得多。数组与指针语句具有十分密切的关系,一般来说,指针比较灵活简洁,而数组则比较直观,容易理解。对于大部分的编译器,使用指针比使用数组生成的代码更短,执行效率更高。

2022-04-18 10:37

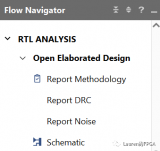

Verilog与ASIC设计的关系 Verilog作为一种硬件描述语言(HDL),在ASIC设计中扮演着至关重要的角色。ASIC(Application Specific Integrated Circuit,专用集成电路)设计是一个复杂的过程,涉及到逻辑设计、综合、布局布线、物理验证等多个环节。在这个过程中,Verilog被用来描述数字电路的行为和结构,进而实现ASIC的设计。 具体来说,Verilog在ASIC设计中的作用主要体现在以下几个方面: 逻辑设计 :使用Verilog可以描述数字电路的行为和逻辑结构,包括输入输出端口

2024-12-17 09:52

使用内联函数替换重复的短代码,一方面,可以避免函数的回调,加速了程序的执行,利用指令缓存,增强局部访问性;另一方面,可以方便代码管理。

2024-03-28 10:53

在Vivado FlowNavigator中有一个Elaborated Design,如下图所示,属于RTL Analysis这一步对应的设计。可能很多工程师都没有使用到,而实际上对于代码优化,它是很有帮助的。

2020-10-21 10:56

对于嵌入式系统,最终代码的体积和效率取决于由编译器生成的可执行代码,而非开发人员编写的源代码;但是源代码的优化,可以帮助

2021-11-09 10:31

最近,看到群里的小伙伴在讨论【我的代码不按照流程执行】相关的话题。这类问题,有经验的工程师肯定能想到是什么原因导致的,那就是编译器把你代码优化了。

2023-11-20 10:21