如下图所示,除了时钟信号CLK和数据地址复用信号AD之外,PCI总线至少还应包括FRAME#(用于表示一次数据传输的起始)、C/BE#(Command/Byte Enable)、IRDY#

2018-04-08 08:52

这些信号,以响应复位周期。RST_I被复位(变为0)后的第一个时钟上升沿到来后,主机接口的STB_O和CYC_O信号可以被立即置位(变为1)。

2018-07-11 09:07

所谓的小端模式(Little-endian),是指数据的高字节保存在内存的高地址中,而数据的低字节保存在内存的低地址中,这种存储模式将地址的高低和数据位权有效地结合起来,高地址部分权值高,低地址部分权值低,和我们的逻辑方法一致。

2018-07-22 10:14

何为总线周期,总线周期就是CPU完成一次访问内存或接口操作所需要的时间。

2020-11-30 10:00

EtherCAT总线周期位置,周期速度,周期转矩的模式切换。

2023-11-24 09:13

时钟周期是最小单位,机器周期需要1个或多个时钟周期,指令周期需要1个或多个机器周期;机器

2017-12-08 10:44

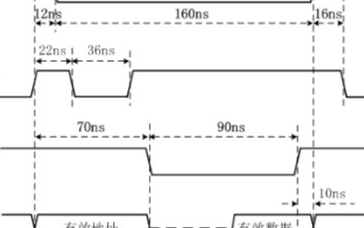

英创公司新近推出的工控主板EM335x支持精简ISA扩展总线。由于主板管脚的限制,ISA总线采用了地址数据复用的方式,在每个总线周期的开始送出地址数据,由ISA_ADV

2020-01-17 10:20

总线时钟周期与CPU时钟周期是计算机体系结构中两个重要但有所区别的概念。为了深入探讨它们之间的区别,本文将从定义、作用、关系、影响因素以及实际应用等多个方面进行详细阐述。

2024-09-26 15:43

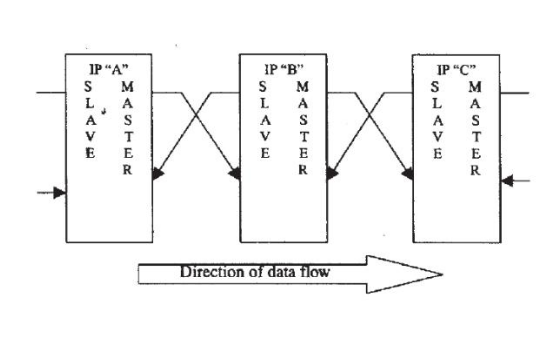

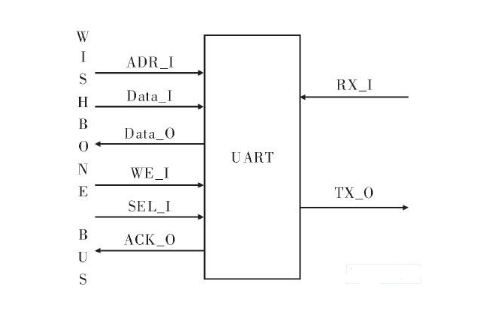

规范。总线规范定义的是IP核之间的通用接口,因此它定义了一套标准的信号和总线周期,以连接不同的模块,而不是试图去规范IP核的功能和接口如何实现。

2018-07-04 09:02

支持用户定义的标签。这些标签可以用于为地址、数据总线提供额外的信息如奇偶校验,为总线周期提供额外的信息如中断向量、缓存控制操作的类型等。Wishbone规范只定义标签的时序,而标签的具体含义用户可自行定义。支持用户定

2018-07-06 08:07