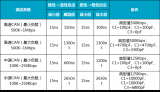

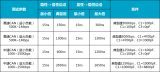

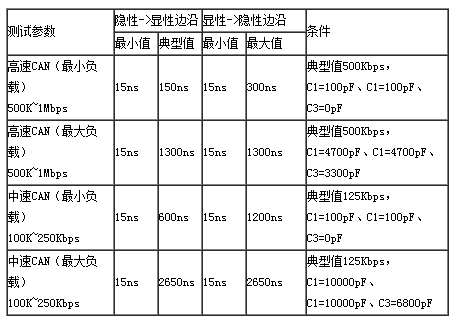

边沿时间分为上升沿时间、下降沿时间。下降沿时间是按照电压(20%~80%电压区间,有些按照10%~90%电压区间测量边沿时间,文中以20%~80%电压区间测量边沿时间)。表中给出时间范围,如果超出

2018-09-22 08:51

边沿触发器,指的是接收时钟脉冲CP 的某一约定跳变(正跳变或负跳变)来到时的输入数据。在CP=l 及CP=0 期间以及CP非约定跳变到来时,触发器不接收数据的触发器。具有下列特点的触发器称为边沿触发方式触发器,简称边沿

2018-01-31 09:02

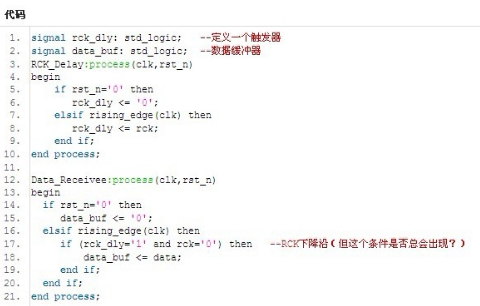

在同步电路设计中,边沿检测是必不可少的!

2017-08-16 15:19

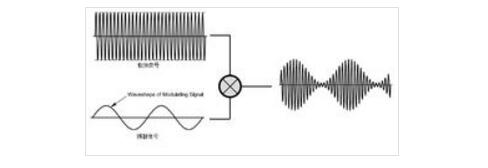

本文首先阐述了单边带的概念、单边带的信号及单边带信号的波形及频谱,其次阐述了双边带的概念及双边带频谱特性,最后介绍了

2018-03-13 15:13

CAN总线边沿时间会影响采样正确性,而采样错误会造成错误帧不断出现,影响CAN总线通信。

2018-11-23 14:04

本文开始介绍了JK触发器工作特性与边沿JK触发器的特点,其次介绍了边沿JK触发器工作原理与特点,最后介绍了集成边沿式JK触发器边沿式JK触发器设计及波形仿真图形。

2018-01-30 17:17

1、什么是边沿检测 边沿检测用于检测信号的上升沿或下降沿,通常用于使能信号的捕捉等场景。 2、采用1级触发器的边沿检测电路设计(以下降沿为例) 2.1、设计方法 设计波形图如下所示: 各信号说明如下

2023-06-17 14:26

以后程序每执行到该边沿指令,用记下的前一次的位逻辑值和当前的位逻辑值,以决定输出结果,同时再记下当前的位逻辑值,供下次使用。

2021-03-24 15:18

“ 本文主要分享了在Verilog设计过程中一些经验与知识点,主要包括Verilog仿真时常用的系统任务、双向端口的使用(inout)、边沿检测”

2022-03-15 13:34

CAN总线设计规范对于CAN节点的信号边沿各项参数都有着严格的规定,如果不符合规范,则在现场组网后容易出现不正常的工作状态,各节点间出现通信故障。具体要求如表 1所示,为测试标准“GMW3122信号边沿标准”。

2019-05-17 15:18