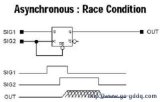

说起亚稳态,首先我们先来了解一下什么叫做亚稳态。亚稳态现象:信号在无关信号或者异步时钟域之间传输时导致数字器件失效的一种现象。

2023-09-19 15:18

亚稳态问题是数字电路中很重要的问题,因为现实世界是一个异步的世界,所以亚稳态是无法避免的,并且亚稳态应该也是面试常考的考点。

2022-09-07 14:28

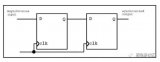

即使 “打两拍”能阻止“亚稳态的传递”,但亚稳态导致后续FF sample到的值依然不一定是符合预期的值,那 “错误的值” 难道不依然会向后传递,从而造成错误的后果吗?

2022-10-19 14:14

在数字电路的设计与实现中,亚稳态是一个不可忽视的现象。它可能由多种因素引发,对电路的稳定性和可靠性产生严重影响。本文将深入探讨数字电路中亚稳态的概念、产生原因、影响以及应对策略,以期为读者提供全面而深入的理解。

2024-05-21 15:29

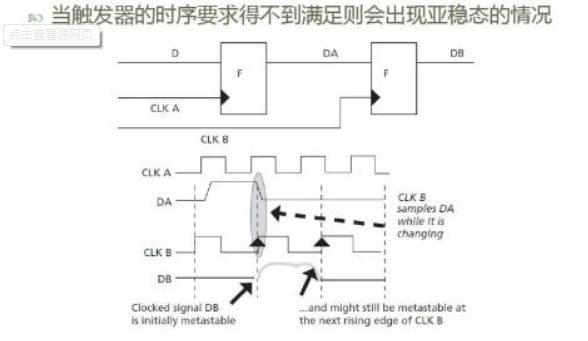

亚稳态是指触发器无法在某个规定时间段内达到一个可确认的状态。

2018-09-22 08:25

亚稳态是我们在设计经常遇到的问题。这个错误我在很多设计中都看到过。有人可能觉得不以为然,其实你现在没有遇到问题只能说明。

2022-10-10 09:30

在复位电路中,由于复位信号是异步的,因此,有些设计采用同步复位电路进行复位,并且绝大多数资料对于同步复位电路都认为不会发生亚稳态,其实不然,同步电路也会发生亚稳态,只是几率小于异步复位电路。

2020-06-26 16:37

通常情况下(已知复位信号与时钟的关系),最大的缺点在于异步复位导致设计变成了异步时序电路,如果复位信号出现毛刺,将会导致触发器的误动作,影响设计的稳定性。同时,如果复位信号与时钟关系不确定,将会导致 亚稳态 情况的出现。

2018-03-15 16:12

在同步系统中,数据始终相对于时钟具有固定的关系 当该关系满足设备的建立和保持要求时,输出将在其指定的传播延迟时间内进入有效状态。

2022-07-03 10:49

亚稳态是指触发器无法在某个规定时间段内达到一个可确认的状态。当一个触发器进入亚稳态时,既无法预测该单元的输出电平,也无法预测何时输出才能稳定在某个正确的电平上。在这个稳定期间,触发器输出一些中间级电平.

2017-12-02 10:40