本文通过对传统大规模集成电路设计流程的优化,得到了更适合于深亚微米工艺集成电路的后端设计流程,详细介绍了包括初步综合、自定义负载线的生成、版图规划、时钟树综合

2009-12-14 11:03

超深亚微米IC设计中的天线效应李蜀霞 刘辉华 赵建明 何春(电子科技大学电子电子科学技术研究院 成都 610054)【摘要】本文主要分析了超深亚微米集成电路设计中天线效

2009-12-19 14:54

随着工艺的发展,器件阈值电压的降低,导致静态功耗呈指数形式增长。进入深亚微米工艺后,静态功耗开始和动态功耗相抗衡,已成为低功耗设计一个不可忽视的因素。针对近

2009-09-15 10:18

基于深亚微米MOS 器件沟道的热噪声浅析曾献芳摘要: 随着 MOS 器件工艺尺寸的不断减小,其不断增高的单位增益截止频率足以满足射频/模拟电路的工作要求。然而,随着沟

2009-12-15 14:31

数字集成电路分析与设计:深亚微米工艺免费下载。

2021-05-12 14:52

摘要:就超深亚微米集成电路中高K栅介质、金属栅、cU/低K互连等相关可靠性热点问题展开讨论.针对超深亚微米集成 电路可靠性问题.提出可靠性设计、生产过程的质量控制、可

2010-04-27 14:13

研究了深亚微米pMOS 器件的热载流子注入(hot2carrier injection ,HCI) 和负偏压温度不稳定效应(negative bias temperature instability ,NBTI) 的耦合效应和物理机制.

2012-04-23 15:35

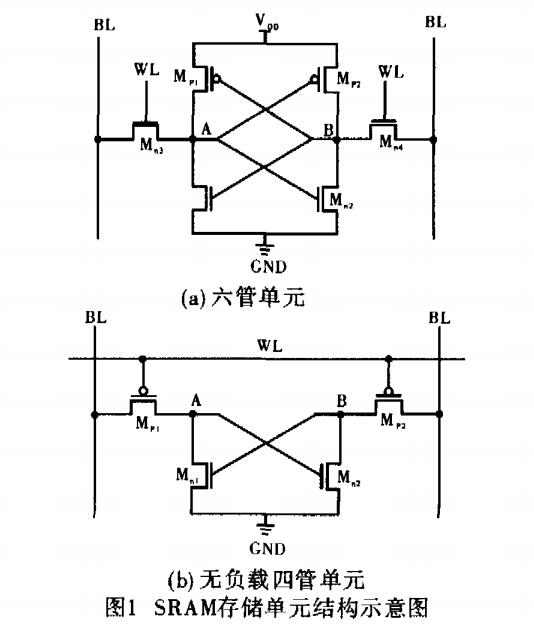

采用基于物理的指数MOSFET模型与低功耗传输域MOSFET模型,推导了新的超深亚微米无负载四管与六管SRAM存储单元静态噪声容限的解析模型.对比分析了由沟道掺杂原子本征涨落引起的相邻MOSFET的阈值电压失配对无负载四管和六管SRAM单元静态噪声容限的影响。

2021-03-26 15:17

主要研究了自动微器件装配系统的定标技术和操纵策略两个问题。在加入了尺度因子优化步骤之后,一种基于Tsai两步法的自定标方法实现了亚微米级的定标精度,并且获得了更加可信的定标角度参数.

2017-09-20 16:10

摘要:增强测试质量和抑制测试代价是超深亚微米集成电路测试及可测性设计领域的两个研究主题。本文介绍了一个基于Mentor公司可测性设计工具的面向多种故障模型的超深亚微

2010-06-07 11:01