FPGA实现除法的方法有几种,比如直接用/来进行除法运算,调用IP核进行除法运算,但这两种方式都有个共同的问题——都是黑盒子,在进行时序违例处理时,往往不好操作,比如想

2023-07-04 10:03

单片机中的除法也是二进制的除法,和现实中数学的除法类似,是从被除数的高位开始,按位对除数进行相处取余的运算,得出的余数再和之后的被除数一起再进行新的相除取余的运算,直到除不尽为止,因为单片机中的

2018-05-31 08:51

FPGA中的硬件逻辑与软件程序的区别,相信大家在做除法运算时会有深入体会。若其中一个操作数为常数,可通过简单的移位与求和操作代替,但用硬件逻辑完成两变量间除法运算会占用较多的资源,电路结构复杂,且

2018-05-18 01:15

随着FPGA应用范围的不断扩大以及对速度需求的不断提升,集成高速串行模块的FPGA已经应用于市场。以Xilinx的Virtex5系列为代表的集成GTPRocketIO模块的F

2018-07-20 11:42

高速串行通信的“高速”一般比较高,基本至少都会上G。如果利用FPGA内部的LUT、触发器和普通IO是无法满足这样高的输入输出速率的。

2024-08-05 11:12

本文针对由FPGA构成的高速数据采集系统数据处理能力弱的问题,提出FPGA与单片机实现数据串行通信的解决方案。

2017-02-11 14:30

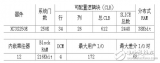

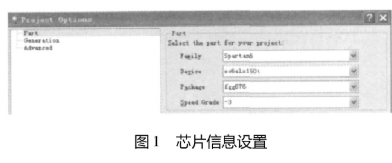

本文主要介绍了基于FPGA的串行A/D转换模块设计,tcl594以8位开关电容逐次逼近A/D转换器为基础而构造的CMOSA/D转换器,用Xilinx公司的FPGA芯片XC3S250ETQG144

2017-12-19 10:48

通常如果需要乘以或除以2n,都可以用移位的方法代替。如果乘以2n,都可以生成左移的代码,而乘以其它的整数或除以任何数,均调用乘除法子程序。用移位的方法得到代码比调用乘除法

2018-03-12 13:56

随着高速数字系统的发展,高速串行数据被广泛使用,内嵌高速串行接口的FPGA也得到大量应用,相应的高速串行信号质量的测试也越来越频繁和重要。通常用示波器观察信号波形、眼图

2020-07-10 10:11

传输系统的组成结构如图1所示,主要由两块ATCA板和一块ATCA机箱背板组成。两块ATCA板上各放置一片FPGA作为串行链路的两个端点,两片 FPGA之间用两对差分线进行连接,形成双向各

2021-05-05 16:49