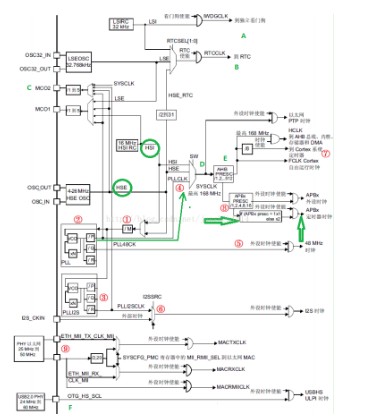

主 PLL 时钟的时钟源要先经过一个分频系数为 M 的分频器,然后经过倍频系数为 N 的

2018-12-26 15:17

本实验活动介绍锁相环(PLL)。PLL电路有一些重要的应用,例如信号调制/解调(主要是频率和相位调制)、同步、时钟和数据恢复,以及倍频和频率合成。在这项实验中,您将建立一个简单的

2023-07-10 10:22

在电子和通信领域,倍频器和锁相环(PLL)是两种常见的电路结构,它们在信号处理、频率合成和通信系统中扮演着重要角色。尽管两者在某些方面存在相似之处,但它们在功能、工作原理和应用领域等方面存在显著差异。本文将对倍频

2024-06-20 11:34

在FPGA设计中,PLL(锁相环)模块作为核心时钟管理单元,通过灵活的倍频、分频和相位调整功能,为系统提供多路高精度时钟信号。它不仅解决了时序同步问题,还能有效消除时钟偏移,提升系统稳定性。本文将深入探讨智多晶PLL

2025-06-13 16:37

多倍频感应耐压原理1.引言变压器线圈的绝缘分为主绝缘和纵绝缘。主绝缘也叫横绝缘是指线圈对它本身以外的其他结构部分的绝缘,包括它对油箱、铁芯、夹件和压板的绝缘,对同一相内其他线圈的绝缘,以及对不同相

2024-01-19 10:20 武汉千旭电力科技有限公司 企业号

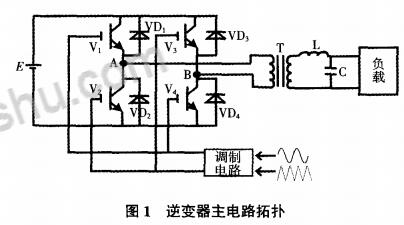

时的开关频率不能过高。本文首先介绍了主电路与三环控制,其次介绍了单极性倍频SPWM调制,最后阐述了系统实验分析wNN,具体的跟随小编一起来了解一下。

2018-05-10 15:32

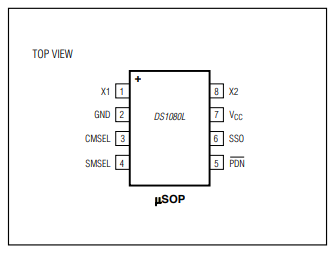

DS1080L是低抖动、基于晶振的时钟发生器,内部集成锁相环(PLL),用于产生16MHz至134MHz的扩频时钟输出。该器件的时钟倍频速率和抖动幅度可通过引脚设置。DS1080L提供扩频禁用模式和关断模式,可节省功耗。

2025-04-15 09:59

噪声系数的定义是输入信噪比比上输出信噪比,即噪声系数是对信号的SNR下降的程度进行衡量。

2024-03-27 15:14

当PLL参考时钟和PLL反馈时钟的频率和相位相匹配时,PLL则被称为是锁定状态。达到锁定状态所需的时间称为锁定时间,这是PLL设计最关键的参数之一。

2018-03-14 15:17

本文介绍了硅的导热系数的特性与影响导热系数的因素。

2025-03-12 15:27