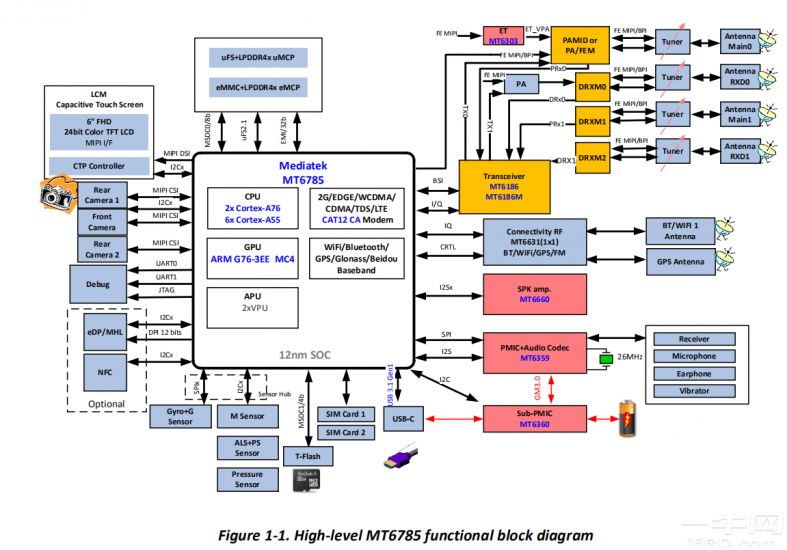

我们知道,不管哪一个平台, 要让CPU跑起来,就必须有一个主时钟,在MTK平台中,这个主时钟多为26 MHz,高通平台则为19.2MHz,其他平台,如ADI Marve

2023-03-16 10:40

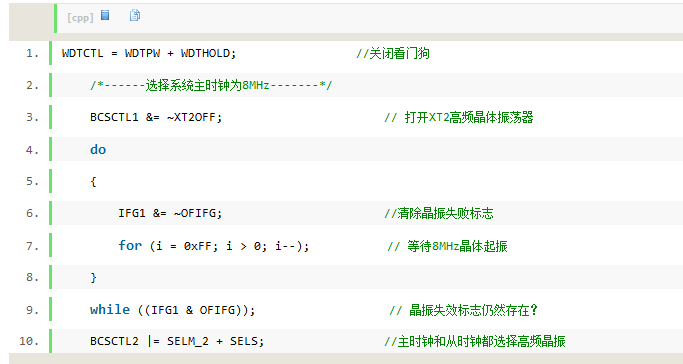

其中MCLK是用给系统使用的,SMCLK用给高速外设使用的,而ACLK主要用给低速外设使用。在系统PUC之后,默认SMCLK与MCLK都以DCO作为时钟源,震荡频率在1.1M左右,ACLK以LFXT1作为时钟源,工作在LF模式下内部6pF的负载电容。

2018-04-22 11:52

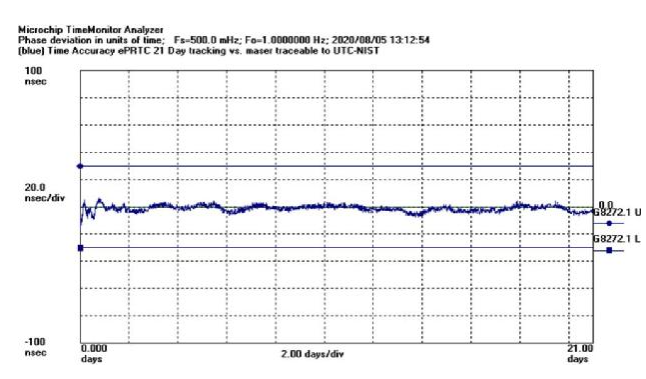

ePRTC的独特设计使其具有最大弹性,能够使用铯钟作为参考时钟保持14天或更长时间,同时在整个长时间中断期内与UTC的最大偏差维持在100 ns。

2020-11-05 16:19

确定了主时钟和衍生时钟后,再看各个时钟是否有交互,即clka产生的数据是否在clkb的时钟域中被使用。

2020-04-06 10:20

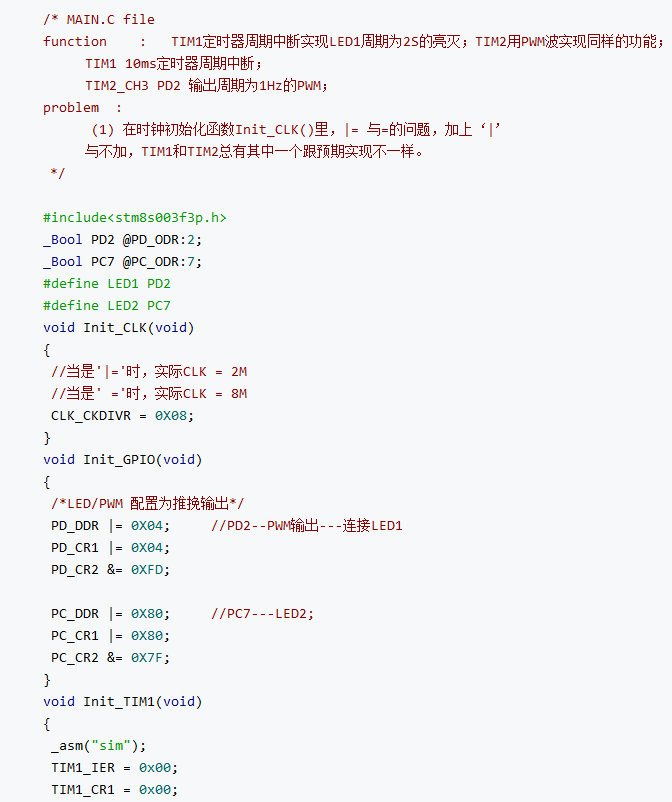

因为STM8S默认使用内部16M高速RC振荡器,且8分频,则系统启动主时钟为2M。即CLK_CKDIVR = 0X18;,如果再去赋值CLK_CKDIVR |= 0X08; 则主

2018-04-16 09:10

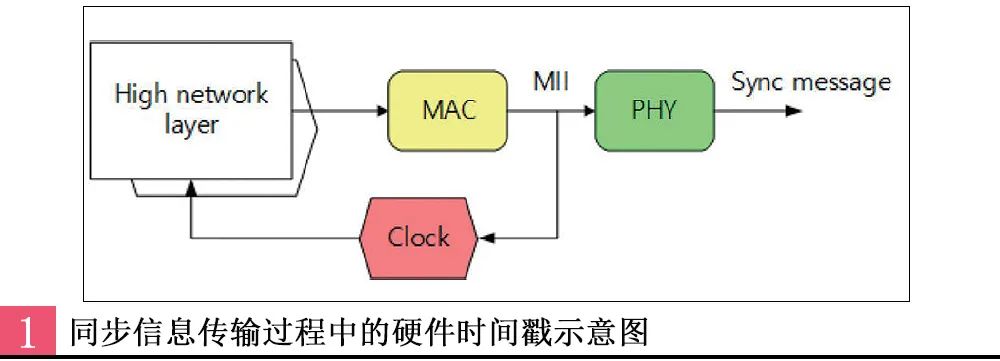

PTP(Precision Time Protocol,精确时间协议)是一种时间同步的协议,由IEEE 1588-2008定义,通过在主时钟和从时钟之间交换信息来工作,用于精确同步分布式网络通信中各个节点的实时

2023-12-04 14:10

目前,大型设计一般推荐使用同步时序电路。同步时序电路基于时钟触发沿设计,对时钟的周期、占空比、延时和抖动提出了更高的要求。为了满足同步时序设计的要求,一般在FPGA设计中采用全局时钟资源驱动设计的

2017-02-11 11:34

//PLL0时钟配置 LPC_SC-》SCS=0X00000020; /*使能外部主晶振,频率范围1-20M*/ if(LPC_SC-》SCS&(1《《5)) /* 主

2018-11-15 16:11

典型的主时钟根包括有以下几种情况:输入端口、千兆位收发器输出引脚以及某些硬件原语输出管脚。

2020-10-13 10:30

众所周知STM32有5个时钟源HSI、HSE、LSI、LSE、PLL,其实他只有四个,因为从上图中可以看到PLL都是由HSI或HSE提供的。 其中,高速时钟(HSE和HSI)提供给芯片主体的主

2023-05-22 10:09