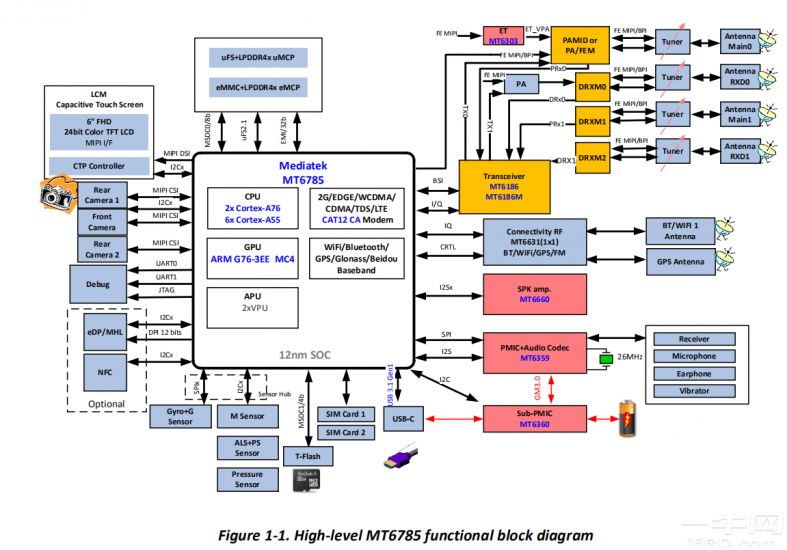

我们知道,不管哪一个平台, 要让CPU跑起来,就必须有一个主时钟,在MTK平台中,这个主时钟多为26 MHz,高通平台则为19.2MHz,其他平台,如ADI Marve

2023-03-16 10:40

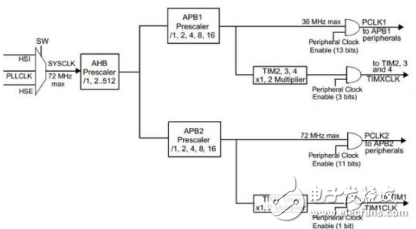

STM32中有多达8个定时器,其中TIM1和TIM8是能够产生三对PWM互补输出的高级定时器,常用于三相电机的驱动,它们的时钟由APB2的输出产生。其它6个为普通定时器

2018-09-03 17:14

这篇主要介绍arm9时钟与定时器方面,根据s3c2440手册第七章的内容来看,涉及到不少的知识点,power管理、时钟、usb时钟、camera等。

2018-02-07 08:38

了解时钟信号的数字定时以及诸如抖动、漂移、上升时间、下降时间、稳定时间、迟滞和眼图等常用术语。本教程是仪器基础教程系列的一部分。发送数字信号其实发送的就是一串由0或1组成的数字序列。 然而,与不同设备进行通信时,

2017-11-17 08:36

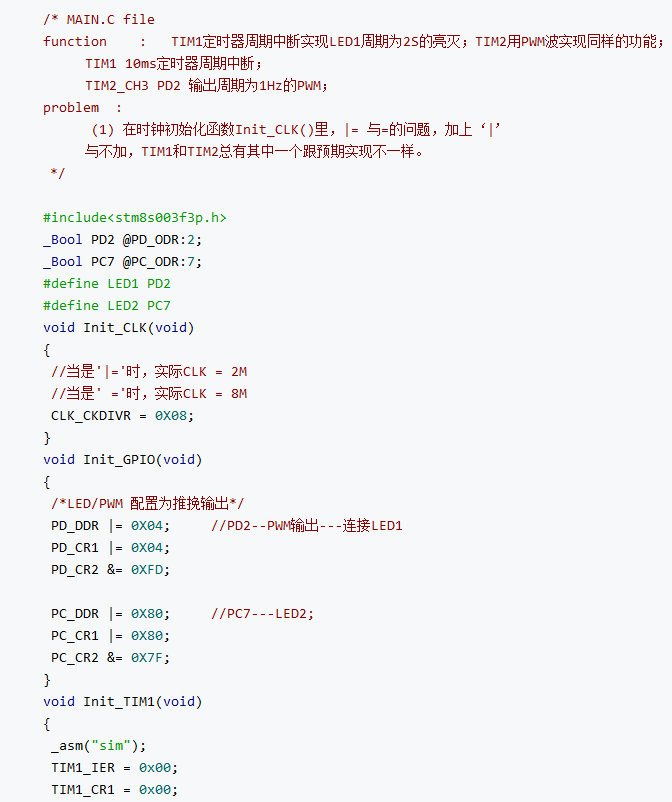

因为STM8S默认使用内部16M高速RC振荡器,且8分频,则系统启动主时钟为2M。即CLK_CKDIVR = 0X18;,如果再去赋值CLK_CKDIVR |= 0X08; 则主

2018-04-16 09:10

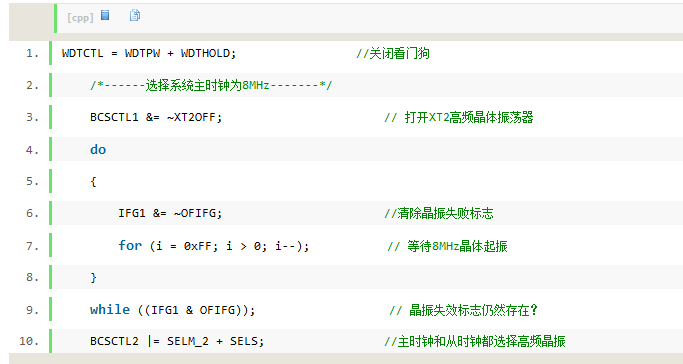

其中MCLK是用给系统使用的,SMCLK用给高速外设使用的,而ACLK主要用给低速外设使用。在系统PUC之后,默认SMCLK与MCLK都以DCO作为时钟源,震荡频率在1.1M左右,ACLK以LFXT1作为时钟源,工作在LF模式下内部6pF的负载电容。

2018-04-22 11:52

确定了主时钟和衍生时钟后,再看各个时钟是否有交互,即clka产生的数据是否在clkb的时钟域中被使用。

2020-04-06 10:20

在测量控制系统中,常常需要实时时钟,以实现定时控制、定时测量或定时中断等。也常需要计数器以实现对外部事件的计数。MCS-51单片机中有两个(增强型有三个)十六位的

2018-02-09 14:00

目前,大型设计一般推荐使用同步时序电路。同步时序电路基于时钟触发沿设计,对时钟的周期、占空比、延时和抖动提出了更高的要求。为了满足同步时序设计的要求,一般在FPGA设计中采用全局时钟资源驱动设计的

2017-02-11 11:34

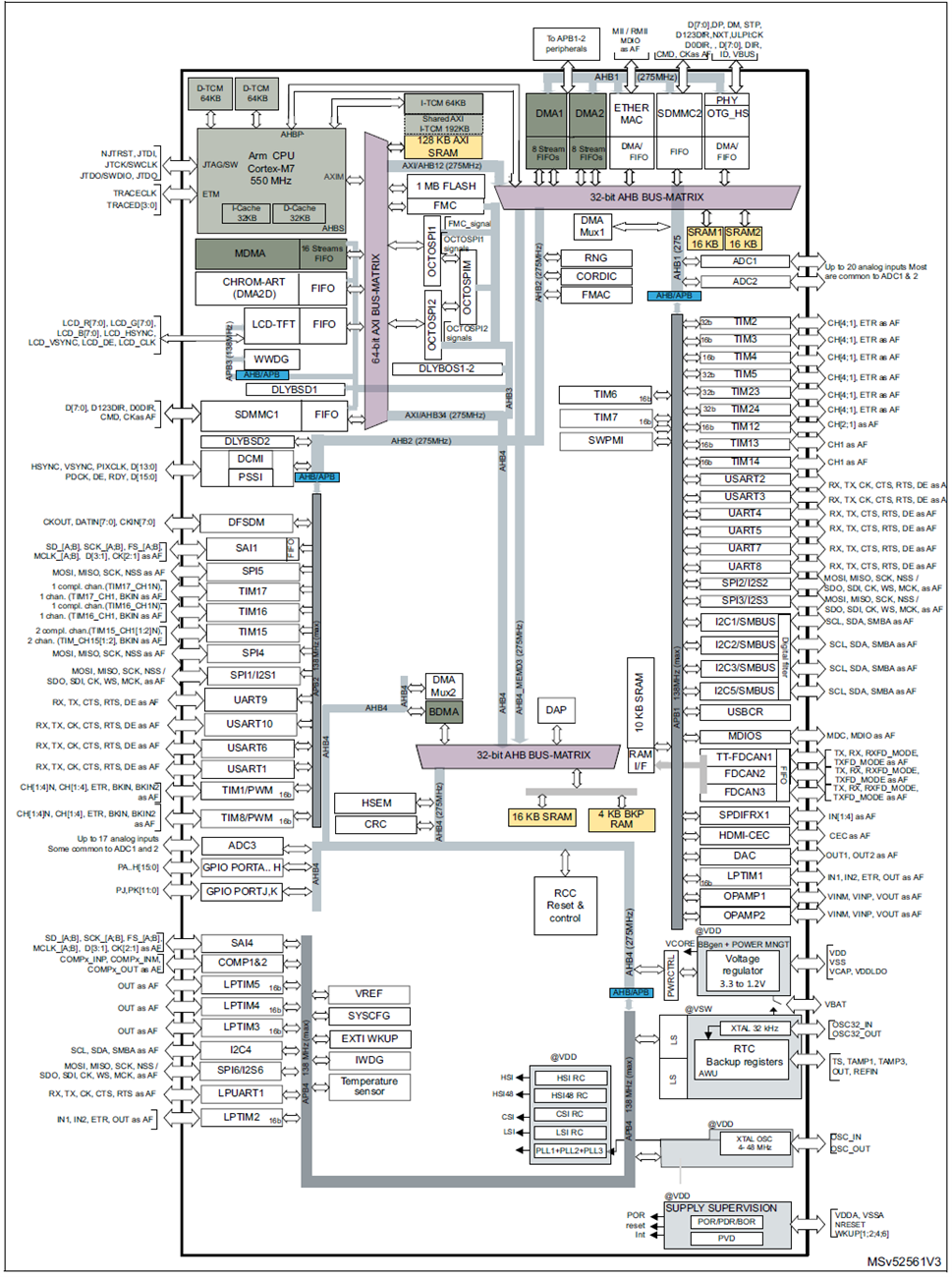

针对常规STM32系列性能测试所引起的准确度低、可靠性差、操作困难等问题,文中提出了一种关于I/O响应频率以及定时器最高频率的极限性能测试方法。通过对STM32H7时钟频率进行最高频率配置,分别

2023-10-24 14:51