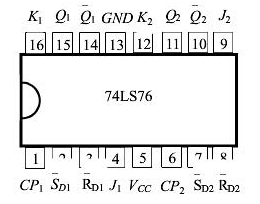

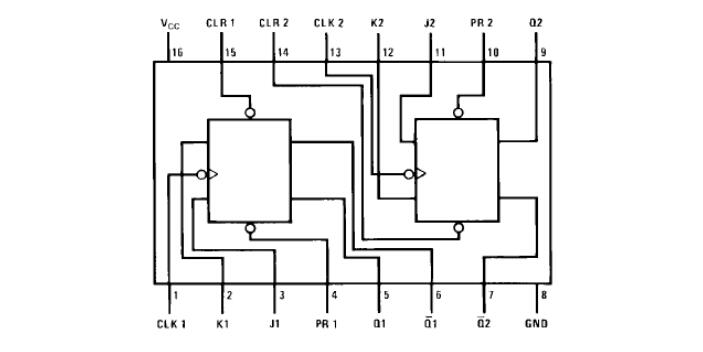

74LS76是双J-K 触发器(负沿触发、带清零和预置)。

2021-07-02 14:23

本文开始介绍了74LS112引脚图与74LS112的功能表,其次介绍了74LS76引脚与封装,最后阐述了74LS112和74LS

2018-04-28 14:44

74LS74内含两个独立的D上升沿双d触发器,每个触发器有数据输入(D)、置位输入( )

2021-06-04 15:40

可以使用“置位复位触发器”指令,根据输入 S 和 R1 的信号状态,置位或复位指定操作数的位。如果输入 S 的信号状态为

2023-06-21 11:45

复位信号在数字电路里面的重要性仅次于时钟信号。对一个芯片来说,复位的主要目的是使芯片电路进入一个已知的,确定的状态。主要是触发器进入确定的状态。在一般情况下,芯片中的每个触发器

2022-09-19 10:07

异步复位信号a是异步复位信号源,异步复位信号b、c、d是到达

2020-06-26 05:36

首选我们来聊聊时序逻辑中最基础的部分D触发器的同步异步,同步复位即复位信号随系统时钟的边沿触发起作用,

2019-07-26 10:17

对于xilinx 7系列的FPGA而言,flip-flop支持高有效的异步复/置位和同步复位/置

2018-07-13 09:31

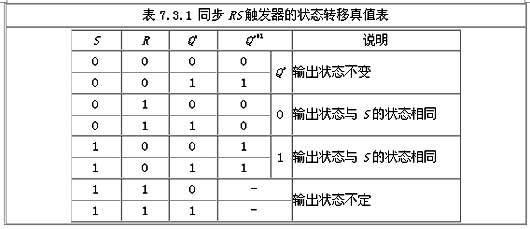

复位/置位触发器(R、S分别是英文复位,置

2021-06-30 17:13

同样值得注意的是,JK 触发器可以通过施加时钟脉冲信号来改变它们的状态。请注意,此时钟信号可以是上升沿或下降沿。此外,74LS76 能够忽略无效输出。

2023-05-05 09:26