时序电路设计串入/并出移位寄存器一 实验目的1掌握VHDL语言的基本描述语句的使用方法。2掌握使用VHDL语言进行时序电路设计的方法。

2009-03-13 19:29

时序电路设计串入/并出移位寄存器一 实验目的1掌握VHDL语言的基本描述语句的使用方法。2掌握使用VHDL语言进行时序电路设计的方法。

2009-03-13 19:29

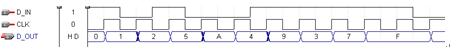

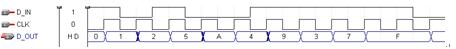

时钟 (CP) 每次由低变高时,数据右移一位,输入到 Q0, Q0 是两个数据输入端(DSA 和 DSB)的逻辑与,它将上升时钟沿之前保持一个建立时间的长度。 主复位 (MR) 输入端上的一个低电平将使其它所有输入端都无效,同时非同步地清除寄存器,强制所有的输出为低电平。

2019-07-15 10:23

代码编译报错信息为process clocking is too complex,不知道代码哪儿错了,求高手指教![code]LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY ser_to_para isPORT(serin,clk,st:IN STD_LOGIC;para:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END ENTITY ser_to_para;ARCHITECTURE behav of ser_to_para isBEGINPROCESS(st,clk)VARIABLE temp:STD_LOGIC_VECTOR(7 DOWNTO 0);BEGINIF(st='1')then IF rising_edge(clk) THENFOR n IN 0 TO 7 LOOPtemp(n):=serin;END LOOP; END IF;para

2014-11-07 15:38

电子类手册,很好的资料,设计师的必备资料。

2016-05-30 15:08

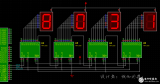

74HC164是高速CMOS电路,管脚与低功耗肖特基TTL(LSTTL)系列兼容。AIP74HC164是8位的串入并出、边沿触发的移位寄存器,

2022-03-08 11:10

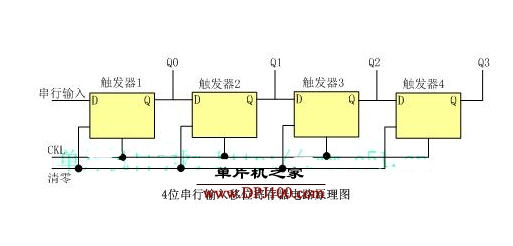

移位寄存器按照不同的分类方法可以分为不同的类型。 如果按照移位寄存器的移位方向来进行分类, 可以分为左移移位寄存器、移位寄存器

2019-07-15 09:38

74HC595和74LS164一样,也是串入并出的移位寄存器。

2018-05-30 11:22

74LS164 器件功能作用 8 位串入,并出移位寄存器

2016-12-09 13:00

8051单片机串行口方式0为移位寄存器方式,外接一个串入并出的移位寄存器,就能扩展一个并行口...

2018-03-15 09:57