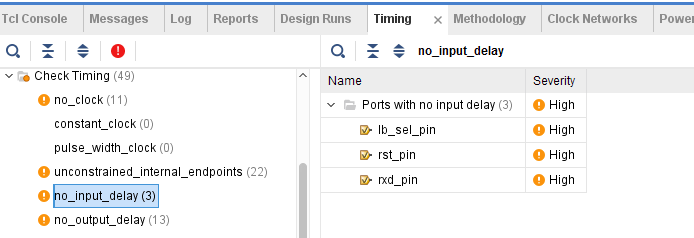

作者:猫叔 延迟约束 对于延迟约束,相信很多同学是不怎么用的,主要可能就是不熟悉这个约束,也有的是嫌麻烦,因为有时还要计算PCB上的走线延迟导致的时间差。而且不加延迟约束,Vivado也只是在

2020-11-14 10:34

09在敷铜上走线不了。规则在哪设置一下。99se的这个功能plow through ploygons打勾就可以的。有大神知道哪里设置的吗???

2019-07-29 05:35

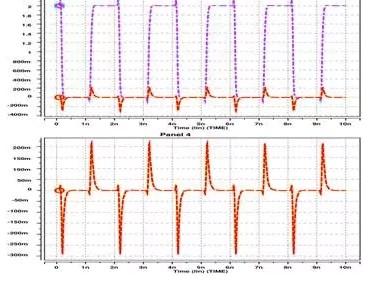

串扰形成的根源在于耦合。在多导体系统中,导体间通过电场和磁场发生耦合。这种耦合会把信号的一部分能量传递到邻近的导体上,从而形成噪声。耦合的方式主要有两种:1、容性耦合。2、感性耦合。

2019-01-07 16:22

电子发烧友网为你提供FR4敷铜板上走线和过孔的电流承载能力的方案和测试资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工

2021-04-05 08:44

文中介绍设计和测试FR4敷铜板上走线和过孔的电流承载能力的方案和测试结果,其测试结果可以为设计人员在今后的设计中提供一定的借鉴,使PCB设计更合理、更符合电流要求。

2022-11-01 16:22

PCB设计时,有时候需要在不增加PCB走线宽度的情况下提高该走线通过大电流的能力(载流能力),通常的方法是给该导线镀锡(或者上锡);下面以在PCB顶层

2019-09-06 15:57

上网找了些案列,查看的时候,发现板子上的走线的网络,器件的管脚网络都没有,请问怎么解决这个问题?

2019-09-19 05:38

题目不知道说啥?没办法,标题不能太长,但是摘要可以。意思是说走线在表层,1到2层介质是低损耗板材,但是2到3层介质是混压的普通损耗板材,这样走线参考到L3层的话,使用低

2023-09-04 15:52

现阶段印制电路板(PCB)的主要材料是FR4的敷铜板,铜纯度不低99.8%的铜箔实现着各个元器件之间平面上的电气连接,镀通孔(即VIA)实现着相同信号铜箔之间空间上的电气连接。

2022-11-09 09:24

本人最近在设计一个板子,视频信号通过sma接口输入到板子上,对于这个信号需要进行一些后续的处理。那么这个cvbs视频信号进来之后对走线有什么要求呢?比如线宽,阻抗匹配,是否包地呢?谢谢

2019-08-29 02:47