为什么要测试芯片上下电功能?芯片上电和下

2023-11-10 15:36

电路设计中,满足MCU的上电时序,是系统设计最基本最重要的要求之一,因此设计中我们会格外关注系统电源的上下电时间,如果

2022-12-20 09:54

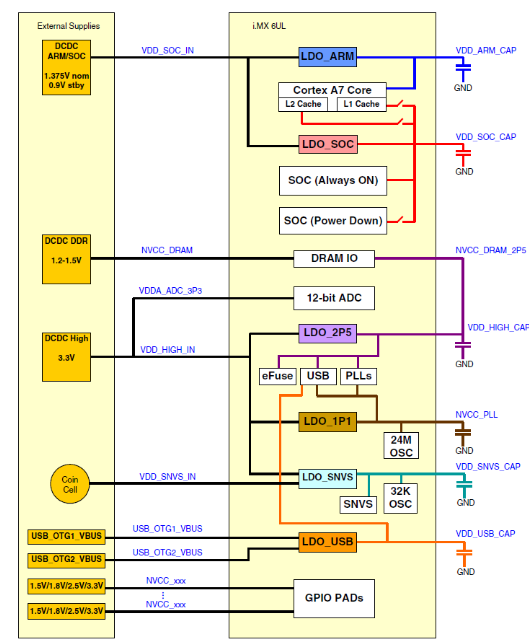

为确保芯片能可靠的工作,应用处理器的上下电通常都要遵循一定时序, 本文以i.MX6UL应用处理器为例,设计中就必须要满足芯片

2018-05-16 18:03

快速上下电时,主控1.8V的GPIO控制的LED会亮一下。放久一点再上电则不会异常亮。仔细排查发现1.8V比0.9V先上

2025-06-18 14:16

当对产品进行快速上下电测试时,若未能满足MCU的上下电要求,MCU往往会出现无法启动甚至锁死的问题。对于单电源供电的MC

2023-08-04 14:30

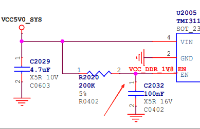

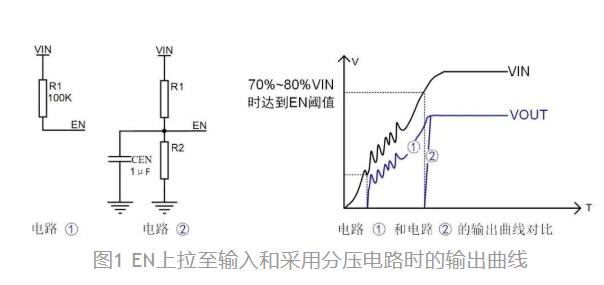

由上电时序可知,VDD_SOC_IN上电时序要迟于VDD_HIGH_IN

2018-04-28 09:57

一:供电电源时序 EMMC 的供电有两种模式,且分两路工作,有 VCC 和 VccQ。在规范上,上电时序是有要求的,如下

2020-10-30 21:29

电路设计中,满足MCU的上电时序,是系统设计最基本最重要的要求之一,因此设计中我们会格外关注系统电源的上下电时间。 如果

2022-08-26 20:23

芯片上电时峰值电流的一种重要方法。首先,选择更低的电源电压,可以减小电源电压与芯片电压之间的压差,从而降低

2023-11-07 10:42

大多数FPGA芯片是基于 SRAM 的结构的, 而 SRAM 单元中的数据掉电就会丢失,因此系统上电后,必须要由配置电路将正确的配置数据加载到 SRAM 中,此后 FPGA 才能够正常的运行。

2019-07-01 17:16