由上电时序可知,VDD_SOC_IN上电时序要迟于VDD_HIGH_IN

2018-04-28 09:57

为什么电源纹波不能直接一键捕获呢?为什么多路上电时序前后分析对比这么麻烦呢?

2017-04-19 10:42

时序以及各阶段I/O 管脚状态,说明了FPGA上电配置对电路功能的严重影响,最后针对不同功能需求的FPGA外围电路提出了有效的设计建议。

2017-11-22 07:18

当遇到系统启动失败的问题时,请先使用示波器检查器件的供电引脚是不是存在上电缓慢,掉电不彻底的情况。

2019-10-10 16:01

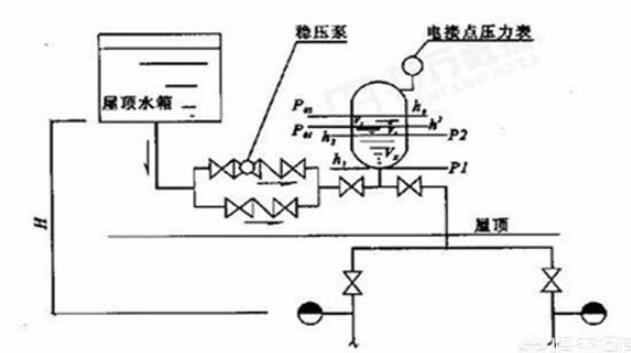

电接点压力表具有测量控制功能,可任意设定上、下控制压力值,动作稳定可靠,在石油、化工、电站、冶金等工业企业及机电设备上广

2020-12-07 16:07

因为ZYNQ 的PS 和PL 部分的电源有上电顺序的要求,在电路设计中,按照ZYQN 的电源要求设计,上电依次为1.0V -> 1.8V -> 1.5 V -> 3.3

2020-01-01 17:27

在正电源管脚V+上的信号建立之前,V+引脚和OUT引脚上的电压为负值。这可能不会损害运算放大器,但若这些信号连接到其他尚未完全供电的芯片上的引脚(例如,假设ADC使用同一V+,其电源引脚一般只能承受最小–0.3 V电

2018-04-10 16:16

丰富的应用特性。这些设备向电源系统提供不同的数字负载,要求使用不同功率等级的多种电压轨,每一种都具有高度个性化的电压轨容差。同样,正确的电源开启和关断时序也很重要。随着时间推移,电路板上电压轨的数量成倍增加,使得电源系统的时

2022-01-21 10:51