三态数据缓冲器是数据输入/输出的通道,数据传输的方向取决于控制逻辑对三态门的控制。本文介绍三态缓冲器的逻辑符号。

2018-01-11 10:42

图5,CMOS传输门,双向传输,当C=0,~C=Vdd,两个MOS管都截止,输入和输出之间呈现高阻态,当C=Vdd,~C=0,如果0

2018-11-12 14:34

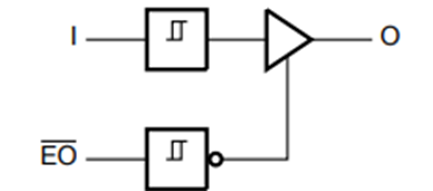

三态逻辑作为一种数字电子技术中的逻辑类型,允许信号线在三种状态之间切换。本文介绍了三态逻辑电路原理并介绍了四种基本类型的三态缓冲器。如果你对

2024-08-01 09:59

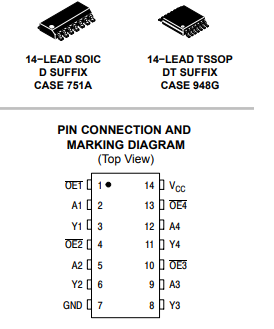

高速CMOS四总线缓冲器MC74VHC125DG带三态控制输入 EDA模型与数据手册分享

2025-05-29 15:02

本文着重探讨 HDIO OBUFT 和 IOBUF 用例。如果含三态控制 (OBUFT/IOBUF) 的 HDIO 输出缓冲器的上电电压为 3.3 V 或 2.5 V 并且 Data(数据)控制信号与 Tristate(三态

2023-07-12 09:50

本文开始介绍了三态门的定义与三态门的应用,其次对三态门的三态及特点进行了介绍,最后阐述了三态输出门电路与

2018-03-01 14:47

什么是时钟缓冲器(Buffer)?时钟缓冲器(Buffer)参数解析 什么是时钟缓冲器(Buffer)?我们先把这个概念搞清楚。 时钟缓冲器就是常说的Clock Buf

2022-10-18 18:36

三态指其输出既可以是一般二值逻辑电路,即正常的高电平(逻辑1)或低电平(逻辑0),又可以保持特有的高阻抗状态。本文开始介绍了三态门的定义,其次介绍了三态门的逻辑符号,最后介绍了

2018-03-01 14:03

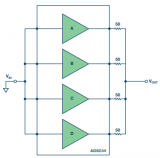

想要降低系统中增加的噪声,必须降低电压噪声。常用方法——并联放置多个缓冲器可降低电压噪声。但是,该方法会使偏置电流、电流噪声、输入电容,统统提高,这时,你需要一款4通道JFET缓冲放大器! 缓冲器是什么? 许多电子电

2018-05-27 05:13