在高性能计算与AI芯片领域,基于SRAM的存算一体(Processing-In-Memory, PIM)架构因兼具计算密度、能效和精度优势成为主流方案。随着存算一体芯片性能

2025-07-11 15:11

为了最大限度地提高Rust应用程序的性能,你需要了解支持代码的底层硬件架构,如何优化算法和数据结构,以及如何对代码进行配置和基准测试。在本文中,我们将简要介绍这些主题,希望能更好地理解如何编写高性能的Rust代码。

2023-11-03 14:28

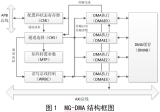

为充分发挥异构多核DSP芯片的实时计算能力,设计并实现了一种高性能多通道的通用DMA,该DMA最大支持64个通道的数据搬运,并支持一维、二维、转置以及级联描述符等多种传输模式。芯片实测传输

2023-11-20 15:52

Stable Diffusion (SD)是当前最热门的文本到图像(text to image)生成扩散模型。尽管其强大的图像生成能力令人震撼,一个明显的不足是需要的计算资源巨大,推理速度很慢

2023-06-12 10:14

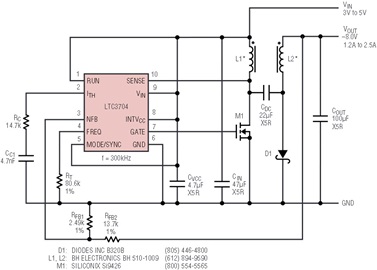

可直接连接至一个从负输出至地的分压器。这种直接连接消除了将反馈信号电平转换到地上通常需要的传统胶水电路,从而节省了空间和费用。LTC3704 在小型 MS10 封装中提供了灵活的高性能操作。

2023-03-10 09:40

可是,设计一个基于FPGA的高性能DNN推理加速器还是充满了困难,它需要寄存器传输级(RTL)编程技巧,硬件验证知识和丰富的硬件资源分配经验等

2018-11-16 10:39

提出一种可进化IP核的设计和实现方法。这种IP核采用进化硬件的设计思想,将遗传算法运用于硬件电路的设计中,使电路能根据当

2021-06-22 14:37

这个库是 Asynchronix 的一个分支,它持续努力地构建用于系统仿真的高性能异步计算框架。 这是一个简洁的异步通道,以快速著称,但也不会在正确性和质量方面取巧。它的性能

2022-10-25 09:50

高层次综合设计最常见的的使用就是为CPU创建一个加速器,将在CPU中执行的代码移动到FPGA可编程逻辑去提高性能。本文展示了如何在Zynq AP SoC设计中使用HLS IP。 在Zynq器件

2017-02-07 18:08