低温漂低功耗的带隙基准源技术设计 摘 要:设计一种低温漂

2010-04-28 08:59

文针对传统基准电压的低PSR以及低输出电压的问题,通过采用LDO与带隙基准的混合设计,并且采用BCD工艺,得到了一种可以

2011-08-23 10:28

1.184 V,启动时间为0.5 μs,电源电压抑制比为-85 dB,版图面积为7531.9 μm2,并且能够集成于高速DAC芯片内部的带隙基准电压源。此

2018-03-05 10:45

传统的带隙电压基准源面积大、功耗大、不适应低功耗小面积的要求。本文立足于

2011-10-09 11:22

带隙是导带的最低点和价带的最高点的能量之差。也称能隙。带隙越大,电子由价

2017-11-24 15:45

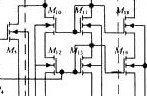

本文为大家介绍一个cmos无运放带隙基准源电路。

2018-01-11 16:52

设计了一款带隙基准电压源,在LTspice下画出原理图,产生网表后,在Hspice下仿真,结果表明,温度系数为9.14×

2011-08-19 11:12

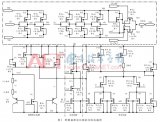

一种低功耗高PSRR的基准电压源 一般基于自偏置的基准电路,由于MOS

2009-11-11 10:07

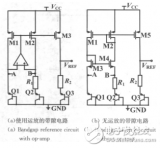

带隙基准电压源的目的是产生一个对温度变化保持恒定的量,由于双极型晶体管的基极电压VBE,其温度系数在室温(300 K)时

2011-11-23 09:19

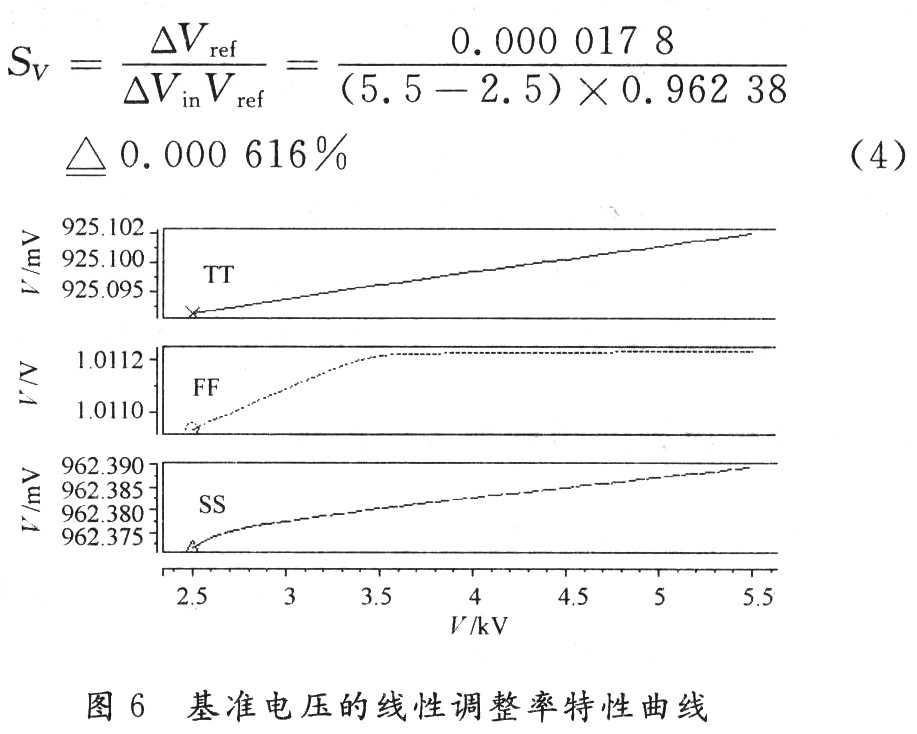

通过一阶、二阶、高阶以及分段等方式进行补偿,来提高基准源的精度[1]。本文基于一阶补偿后的基准电压输出特性,设计

2018-06-26 08:06