对于 FPGA 来说,要尽可能避免异步设计,尽可能采用同步设计。 同步设计的第一个关键,也是关键中的关键,就是时钟树。 一个糟糕的时钟树,对 FPGA 设计来说,是

2020-11-11 09:45

,为什么有些路径在分析时忽略了?我怎么去定位这些约束是哪里设定的? 事实上,Vivado集成设计环境提供了很多辅助工具来协助用户完成时序约束的分析。 本文结合一个具体案例,阐述了如何追溯同一时钟域内partial false path的来源,希望为开发者的设计调试

2021-08-23 11:31

汽车影音导航接收器能够送出非常精确的时间信息,但该信息是固定不变的。它必须经过转换后才能满足系统内已经使用或将要使用的各种装置对同步源的要求。

2011-01-22 10:36

主板时钟电路检修 一、时钟电路的构成及工作原理

2009-04-26 15:53

使用多个时钟时,如何改善系统性能?在使用同一时钟源产生多个时钟时,一个常见的问题是噪声,通常表现为存在于噪底之上的杂散,这是因为单

2017-02-16 01:09

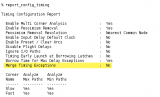

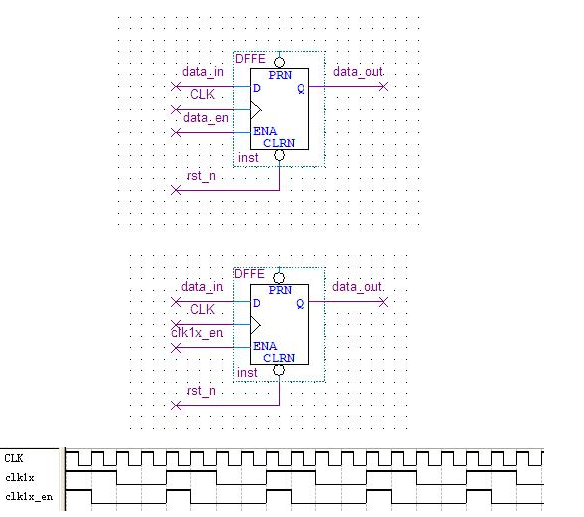

时钟使能电路是同步设计的基本电路,在很多设计中,虽然内部不同模块的处理速度不同,但由于这些时钟是同源的,可以将它们转化为单一时钟处理;在ASIC中可以通过STA约束让分频始终和源

2023-01-05 14:00

时钟使能电路是同步设计的重要基本电路,在很多设计中,虽然内部不同模块的处理速度不同,但是由于这些时钟是同源的,可以将它们转化为单一的时钟电路处理。

2020-08-06 10:35

有一个有趣的现象,众多数字设计特别是与FPGA设计相关的教科书都特别强调整个设计最好采用唯一的时钟域。

2020-09-24 10:20

卫星同步时钟系统是航空交通重要的组成部分之一,其主要作用是为乘客和工作人员提供准确的时间信息,同时卫星同步时钟系统要为其他子系统提供统一的

2023-11-03 14:40

有一个有趣的现象,众多数字设计特别是与FPGA设计相关的教科书都特别强调整个设计最好采用唯一的时钟域。

2023-12-22 09:04