有一个有趣的现象,众多数字设计特别是与FPGA设计相关的教科书都特别强调整个设计最好采用唯一的时钟域。

2020-09-24 10:20

xilinx 的 FPGA 时钟结构,7 系列 FPGA 的时钟结构和前面几个系列的时钟结构有了很大的区别,7系列的时钟结构如下图所示。

2022-07-03 17:13

首先肯定是在本时钟域内的clk_en会先变低(invalid),之后才会使得另外时钟域内的clk_en变高(valid),这时另外一个时钟域内的

2020-11-10 15:06

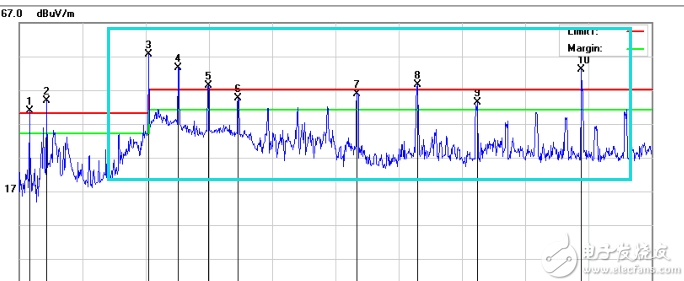

EMI超标的主要源头之一是时钟,良好的时钟设计和布局不仅确保了系统良好的性能和时序问题,还可以最大限度的降低EMI辐射问题。

2018-12-22 14:07

时钟周期也称为振荡周期,定义为时钟频率的倒数。时钟周期是计算机中最基本的、最小的时间单位。在一个时钟周期内,CPU仅完成

2018-03-11 10:07

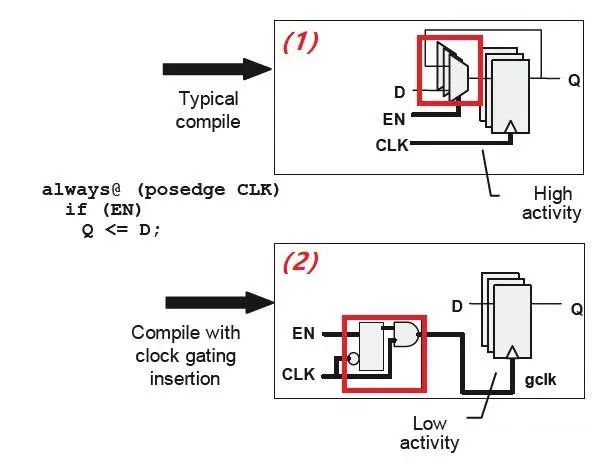

当寄存器组的输出端没有驱动或没有变化时,可以关掉寄存器组的时钟来减少动态功耗,此谓门控时钟 (Clock Gating, CG) 技术。

2023-03-29 11:37

最近搞了个新玩意,不过还是个时钟……

2018-08-14 17:03