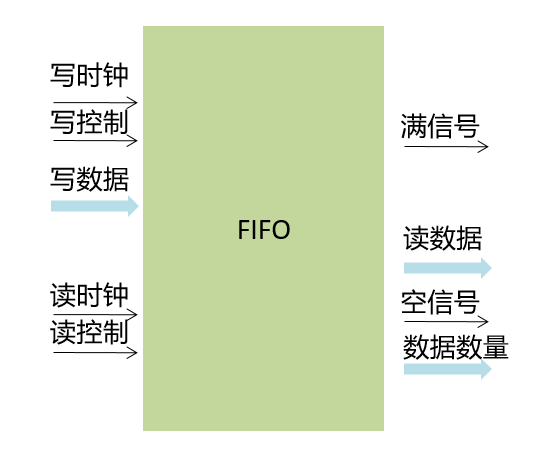

FIFO: First in, First out代表先进的数据先出,后进的数据后出。Xilinx在VIVADO里为我们已经提供了FIFO的IP核, 我们只需通过IP核例化一个FIFO,根据

2021-01-22 09:45

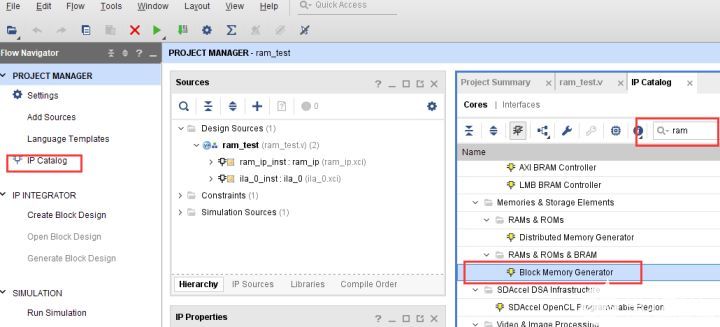

RAM是FPGA中常用的基础模块,可广泛用于缓存数据的情况,同样它也是ROM,FIFO的基础。本实验将为大家介绍如何使用FPGA内部的RAM以及程序对该RAM的数据

2021-01-22 09:43

既然是ROM,那么我们就必须提前给它准备好数据,然后在FPGA实际运行时,我们直接读取这些ROM中预存储好的数据就行。Xilinx FPGA的片内ROM支持初始化数据配

2021-01-22 09:44

基于 Xilinx 公司ZYNQ Ultrascale+ MPSoC系列 FPGA 芯片设计,应用于工厂自动化、机器视觉、工业质检等工业领域

2022-11-02 14:35

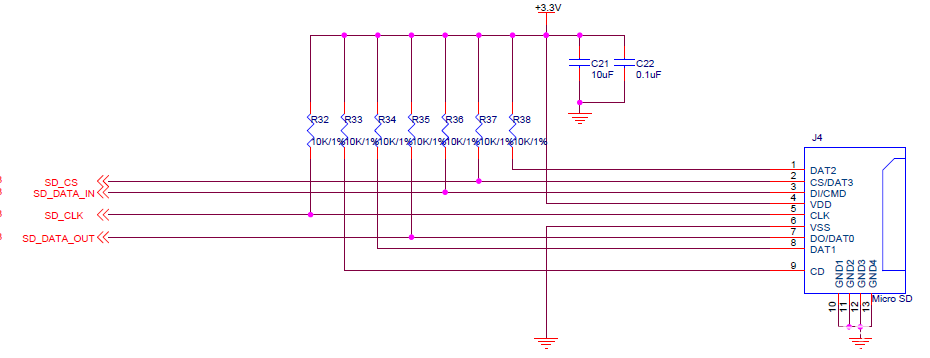

SD卡是现在嵌入式设备重要的存储模块,内部集成了nand flash控制器,方便了主机的的管理。本实验主要是练习对sd卡的扇区进行读写,通常sd卡都有文件系统,可以按照文件名和目录路径来读写文件,但

2021-02-05 11:35

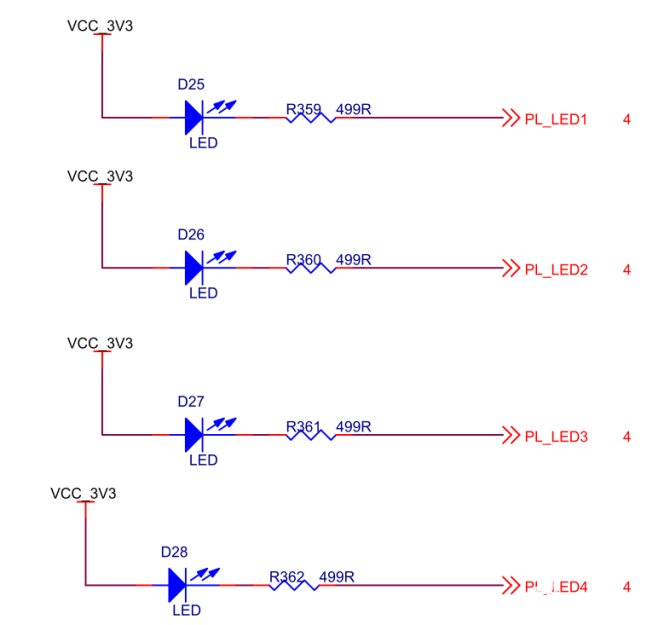

对于ZYNQ来说PL(FPGA)开发是至关重要的,这也是ZYNQ比其他ARM的有优势的地方,可以定制化很多ARM端的外设,在定制ARM端的外设之前先让我们通过一个LED例程来熟悉PL(

2021-01-21 13:28

Zynq MPSoC是Zynq-7000 SoC(之后简称Zynq)的进化版本。Zynq是赛灵思发布的集成PL(

2022-08-15 09:16

Zynq®UltraScale+™MPSoC,现已开始发售。视频向您重点介绍了Xilinx UltraScale +产品组合的第一位成员

2018-11-27 06:47

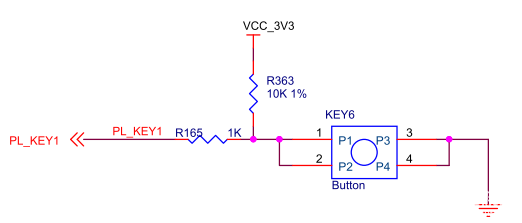

按键是FPGA设计当中最常用也是最简单的外设,本章通过按键检测实验,检测开发板的按键功能是否正常,并了解硬件描述语言和FPGA的具体关系,学习Vivado RTL ANALYSIS的使用。

2021-01-22 09:46

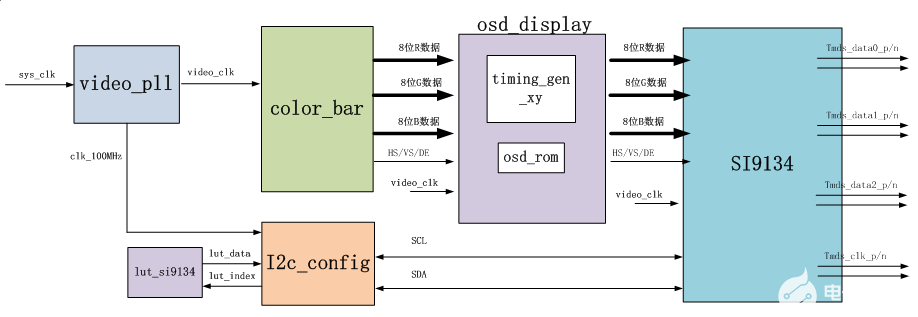

在HDMI输出实验中讲解了HDMI显示原理和显示方式,本实验介绍如何使用FPGA实现字符显示,通过这个实验更加深入的了解HDMI的显示方式。

2021-01-25 09:52